# 金屬化製程

### 目標

- 解釋金屬化製程的原件運用

- 列出最常用的三種材料

- 列出三種金屬沉積的方法

- 描述濺鍍製程

- 解釋在金屬沉積製程中高真空需求的目的

### 金屬化

- 定義

- 運用

- PVD vs. CVD

- 方法

- 真空

- 金屬

- 過程

- 未來趨勢

### 金屬化

• 在晶圓表面上沉積金屬薄膜的過程

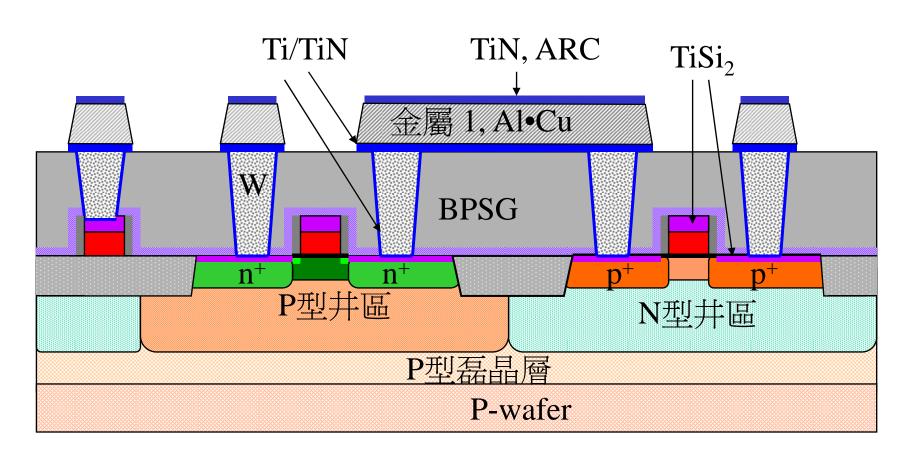

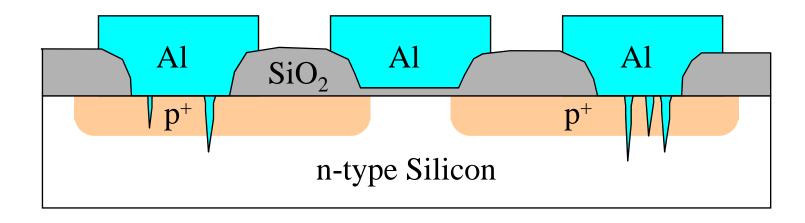

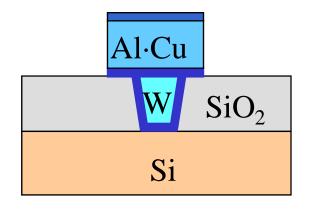

### CMOS: 標準金屬化

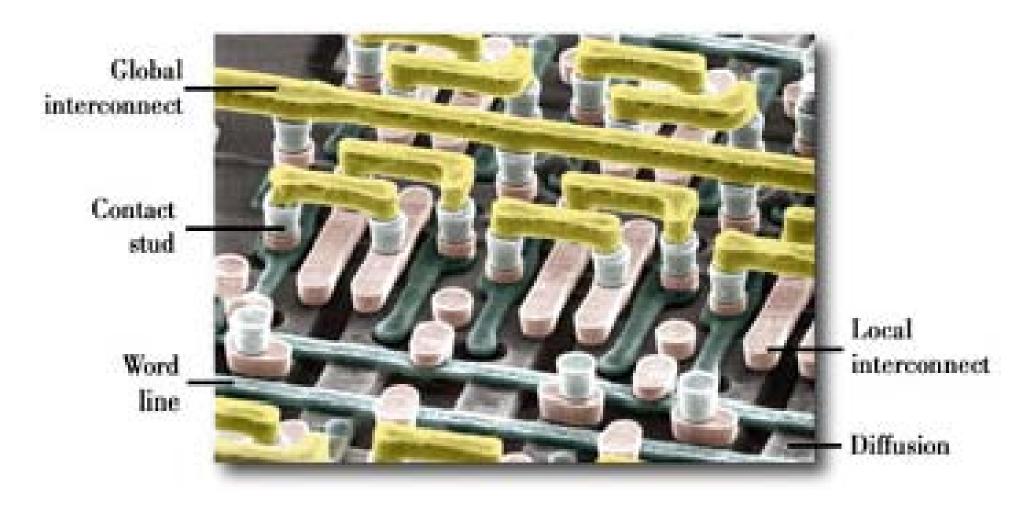

## 運用:相互連接

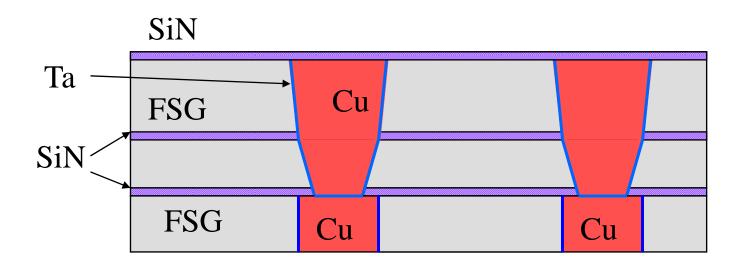

### 以銅當導線的IC晶片剖面圖

### 運用:閘極和電極

- 鋁閘極與電極

- 多晶矽用來取代鋁當閘極金屬

- 矽化物

- 矽化鎢

- 矽化鈦

- 矽化鈷,矽化鉬,矽化鉭,...

- 白金,金,…當DRAM電容器的電極

### Q & A

- 我們可以用相同比率縮短金屬相互連結的尺寸嗎??

- $R = \rho l/wh$ . 當縮短所有尺寸 (長度 l, 寬度 w, 高度 h) 相對的也會縮短原件的特徵尺寸,電阻R會增加

- 電流慢和較大的功率損耗

### 多晶矽

- 閘極與局部連線

- 從70年代中期取代鋁

- 高溫穩定性

- 佈值後的高溫退火製程

- 鋁閘極不能適用上述製程來自我對準的源極/汲極

- 大量參雜

- 在LPCVD 來沉積形成

### 鋁

- 大多數使用的金屬

- 有四種最好的傳導率金屬

- 銀

1.6  $\mu\Omega$ ·cm

- 銅

1.7  $\mu\Omega$ ·cm

- 金

$2.2 \, \mu\Omega \cdot cm$

- 鋁

$2.65 \,\mu\Omega\cdot\text{cm}$

• 在70年代中期前,被用來當閘極

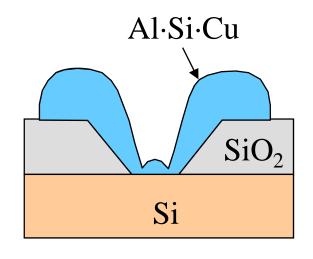

### 鋁矽合金

- 鋁可以直接與矽在源極/汲極接觸

- 矽可以溶解在鋁內且鋁可以擴散進入矽內

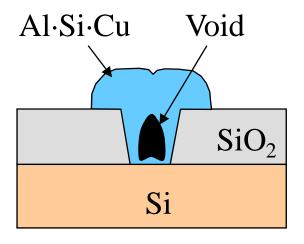

- 連接尖凸物

- 鋁的尖凸誤會穿透參雜接面

- 源極/汲極與基片形成短路

- 大約爲1%的矽參雜入鋁

- 在攝氏400度時的加熱退火會在矽-鋁介面形成矽鋁合金

### 尖凸現象

### 電遷移效應

- 鋁是一種多晶態材料

- 很多小型的單晶態晶粒

- 電流流過鋁線

- 電子將會不斷轟擊晶粒

- 小晶粒將會開始移動

- 這效應稱爲電遷移效應

### 電遷移效應

- 電遷移會扯裂金屬線

- 在剩餘導線有高密度電流

- 使電子轟擊更嚴重

- 造成更遠的鋁晶粒遷移

- 最後造成金屬線的崩潰

- 影響IC晶片的可靠度

- 鋁金屬線: 對老房子引起火災

### 電遷移抵抗

- 當少量的銅與鋁形成合金,鋁的電遷移阻 抗會被顯著地改善

- 鋁矽銅合金被使用

- 鋁銅(0.5%)合金最常被使用

### 鋁金屬沉積

#### • PVD

- 濺鍍

- 蒸鍍

- 加熱

- 電子東

#### • CVD

- 乙烷清化鋁 [DMAH, Al(CH<sub>3</sub>)<sub>2</sub>H]

- 加熱製程

#### PVD vs. CVD

- CVD: 表面化學反應

- PVD:表面沒有化學反應

- CVD: 較好的階梯覆蓋 (50% to ~100%) 和間隙填充能力

- PVD: 較差階梯覆蓋 (~ 15%) 和間隙塡充 能力

#### PVD vs. CVD

• PVD: 品質較高,純沉積薄膜,高傳導率,容 易沉積合金

• CVD: 薄膜總是不純, 低傳導率, 不易沉積 合金

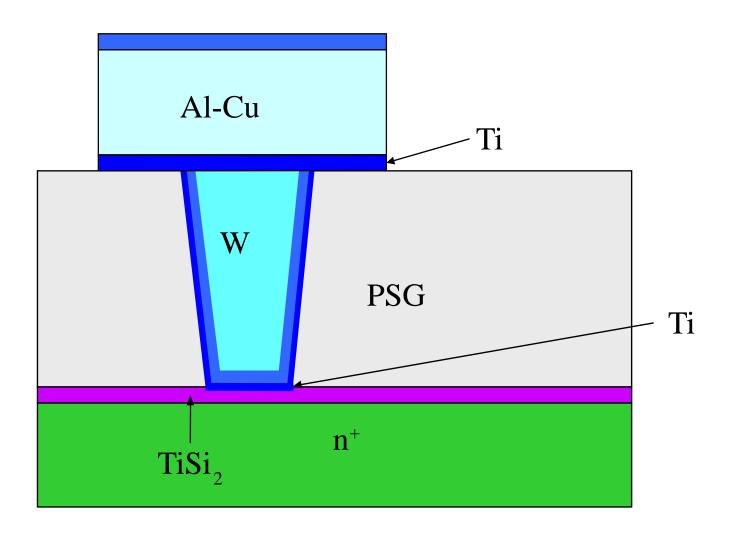

# 鈦的運用

### 氮化鈦

- 阻擋層

- 防止鎢擴散

- 附著層

- 幫助鎢附著在氧化矽表面

- 抗反射層鍍膜 (ARC)

- 減低反射且改進金屬圖案化製程中之微影技術的解析度

- 防治小丘狀凸出物的產生並控制電遷移

- 氮化鈦可藉由 PVD 和 CVD沉積

### 氮化鈦 PVD

- 阻擋層,附著層,抗反射層鍍膜 (ARC)

- 在氫氣與氮氣中濺鍍鈦靶材

- 在電漿中,氮分子會分離

- 放射狀的氮自由基

- 氮離子和鈦反應形成氮化鈦沉積在鈦的表面

- 氫離子會將氮化鈦轟擊離開靶材表面,而將他 們沉積在晶圓表面

### 氮化鈦 CVD

- 阻擋層與黏著層

- 比PVD有較好的階梯覆蓋

- 低溫金屬有機CVD製程Metal organic process (MOCVD)

- ~350 °C

- TDMAT,  $Ti[N(CH_3)_2]_4$

- 不同運用

### 鎢

- 金屬栓塞在接觸窗孔

- 接觸窗口變得更小更窄

- PVD 鋁合金: 較差的階梯覆蓋與孔洞

- CVD 鎢: 非常好的階梯覆蓋看孔隙填充

- 較高的電阻率: 8.0 ~ 12 μΩ·cm 比 PVD 鋁 銅合金 (2.9 ~ 3.3 μΩ·cm)還高

- 只用來連接不同層間的栓塞和局部連線用

### 接觸窗金屬化製程的演變

大開口的接觸窗 PVD金屬可填入

小開口的接觸窗 使用PVD金屬 填入情形

使用CVD鎢塡入 小開口的接觸窗

### 鷂 CVD

- WF<sub>6</sub> 當作鎢原材料

- 和 SiH<sub>4</sub> 產生反應並沉積鎢

- 和 H<sub>2</sub> 產生鉅量鎢沉積在攝氏400度

- 需要一層氮化鈦來幫助鎢附著在二氧化 矽上

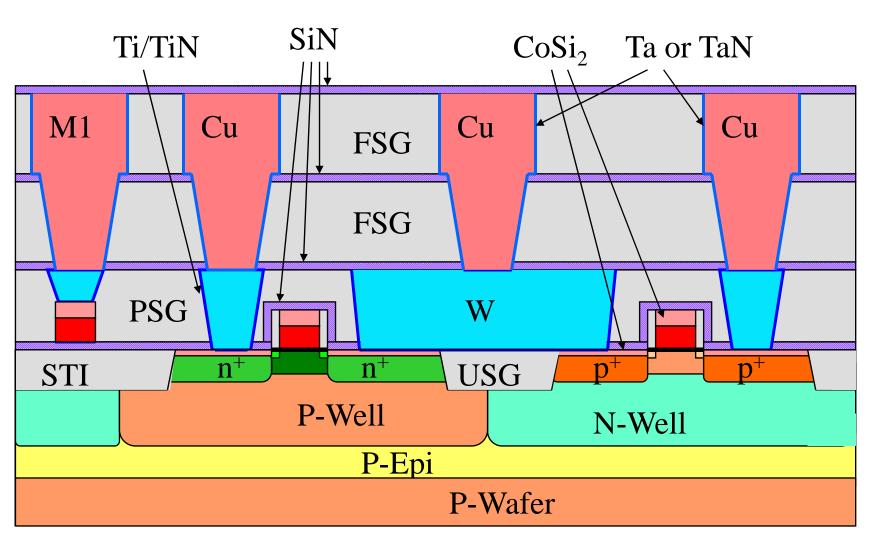

### 銅

- 低電阻率 (1.7 μΩ·cm),

- 減少功率損耗和提高IC速度

- 高電遷移抵抗力

- 高可靠度

- 不易附著在二氧化矽

- 高擴散,和嚴重的金屬污染

- 非常難進行乾蝕刻

- 銅-鹵素化合物的揮發性很低

### 銅沉積

- 種晶層的濺鍍沉積

- CVD或電化學電鍍沉積法

- 退火製程通常是巨量銅沉積進行

- 增進晶粒的尺寸

- 改進導電率

### 鉭

- 阻擋層

- 防止銅擴散

- 濺鍍來沉積

### 金屬薄膜特性

- 厚度

- 應力

- 反射性

- 薄片電阻

### 金屬薄膜特性

- 穿透式電子顯微鏡(TEM)與掃描式電子顯 微鏡 (SEM)

- 剖面圖

- 四點探針

- X光繞射儀(XRF)

- 聲學量測 (Acoustic measurement)

## 穿透式電子顯微鏡(TEM)與 掃描式電子顯微鏡(SEM)

• 穿透量測

• TEM: 非常薄膜,一百多埃

• SEM: 膜厚數百埃

### Q & A

- 爲什麼SEM的相片通常是黑白的?

- 兩次的電子發射時的強度

- 強烈或微弱的訊號

- 相片上的明亮點和晦暗點

- SEM 相片在被分析拍下後以人工上色

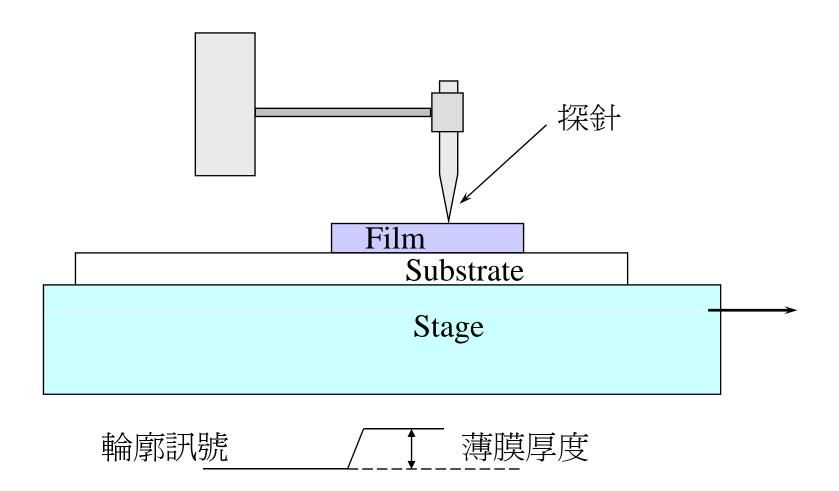

### 輪廓量測器

- 較厚的薄膜 (> 1000 Å),

- 在量測前需要執行圖案化蝕刻製程

- 探針尖端感測器和紀錄細微的表面輪廓

### 輪廓量測器示意圖

### 四點探針

- 量測薄片電阻

- 通常藉由量測薄片電阻,計算出已知薄膜厚度的薄膜電阻率,或計算出薄膜厚度

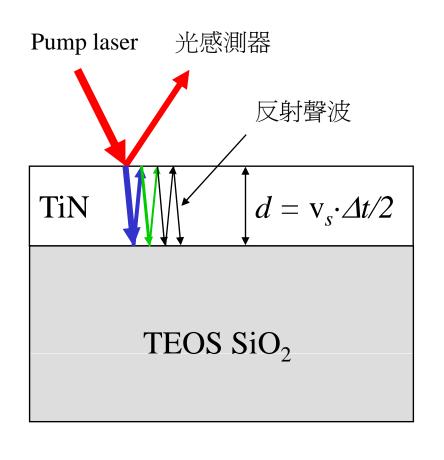

### 聲學量測

- 新技術

- 直接量測不透光的薄膜厚度

- 非直接接觸,可以用來量測晶圓

#### 聲學量測

- 雷射光射在薄膜表面

- 光感測器則量測其反射強度

- 0.1 ps 雷射脈衝,瞬間蝦熱攝氏5~10度

- 熱膨脹會產生聲波

- 他將會在薄膜內傳導且不同材料的表面反射回來

- 當這個回聲到薄膜表面時造成反射係數的改變

#### 聲學量測

- 聲波會在薄膜內來回產生回音

- 這薄膜的厚度可以被計算

$$d = V_s \Delta t/2$$

- $V_s$ 是音速且 $\Delta t$ 是反射係數高峰間的時間改變量

- 這回音衰退率與薄膜的密度有關

- 多層結構薄膜厚度

### 聲學量測金屬薄模示意圖

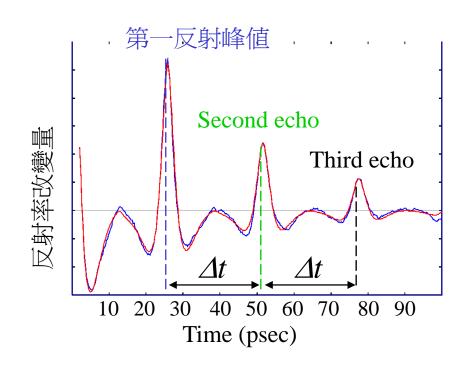

### 氮化鈦厚度

- $d = V_s \cdot \Delta t/2$

- Sound velocity in TiN film  $V_s = 95 \text{ Å/ps}$

- $\Delta t \approx 25.8 \text{ ps}$

- d = 1225 Å

#### 均勻性

- 厚度的均匀(事實上是指非均匀性),薄片 電阻,和反射係數在製程的發指與維護上 都被例行的檢視著

- 可以藉由多個位置的薄片電阻和反射係數而計算出均勻性

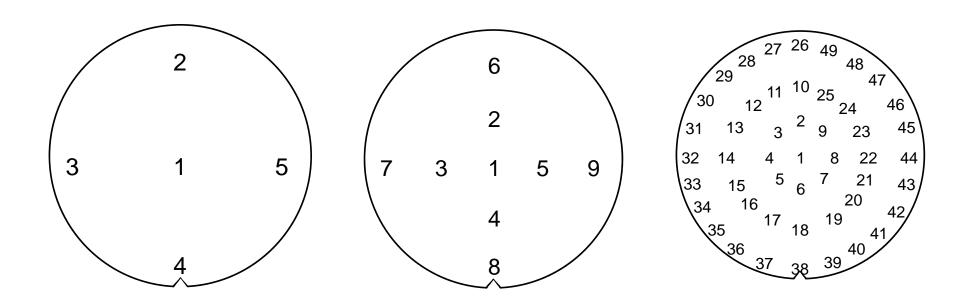

## 均勻性量測的取點分佈

### 均勻性

- 在半導體工業中對製程評鑑最普遍的定 義就是49點量測及標準差 3σ

- 清楚的定義非均勻性

- 對同一組量測資料而言,不同的定義會引起不同的非均勻性結果

- 5點和9點量測最常被使用在製程監視和控制上

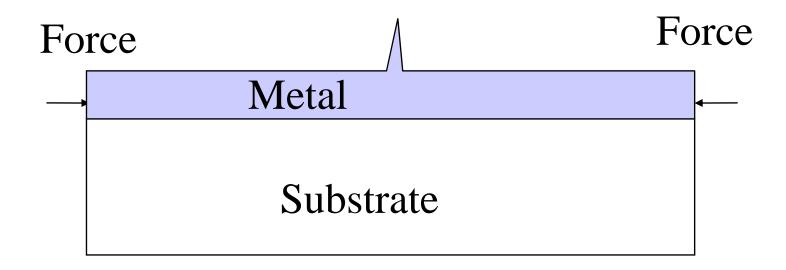

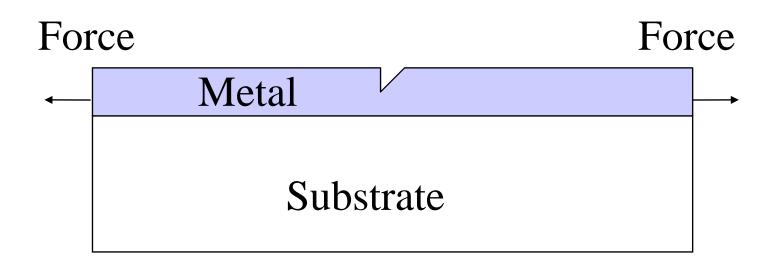

#### 應力

- 因為薄膜與基片之間的材料不匹配所引起

- 收縮應力或伸張應力

- 高壓縮應力會引起小丘狀凸出物

- 這會使不同層間的金屬線短路

- 高伸張應力會引起連線破裂或脫落

# 收縮應力產生小丘狀凸出物

# 張力產生破裂

#### 熱應力

• 鋁比矽有較高的熱膨脹係數

$$\alpha_{A1} = 23.6 \times 10^{-6} \text{ K}^{-1}, \quad \alpha_{Si} = 2.6 \times 10^{-6} \text{ K}^{-1}$$

- 在室溫時,鋁比矽收縮多

- 在室溫時微小的張力是適當的

- 金屬退火 (~ 450 °C)

- 介電質沉積 (~ 400 °C)

#### Q & A

- 為什麼氧化矽薄膜在室溫時,收縮應力較 受到偏愛?

- 二氧化系的熱膨脹係數( $\alpha_{SiO2} = 0.5 \times 10^{-6} \text{ K}^-$ 1)比矽低

- 如果在室溫時具有張力的,他的張力將會大在後續的加熱製程中

#### 反射係數

- 反射係數改變即表示製程狀況的一個走勢

- 是薄膜的晶粒大小尺寸與表面平滑度的函數

- 較大的晶粒有較低的反射係數

- 越平滑的金屬表面有較高的反射係數

- 簡單,快速,非壞性

- 經常在半導體廠中的金屬區間內進行

#### 薄片電阻

- 四點探針

- 廣泛地用來量測薄膜厚度

- 假設晶圓電阻是一樣的

- 比輪廓量測,SEM,聲學量測快且便官

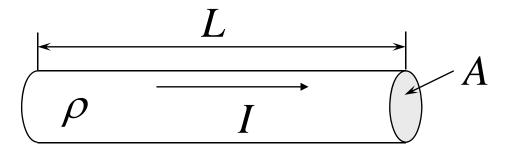

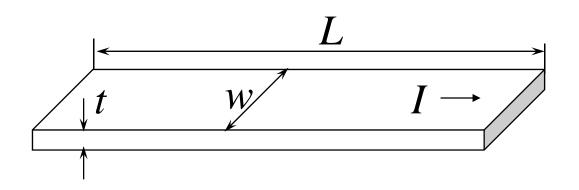

### 薄片電阻

• 薄片電阻 (R<sub>s</sub>) 的定義

$$R_s = \rho/t$$

• 藉由計算  $R_s$ ,可以算出厚度已知的薄片電阻係數,反之亦然

#### 金屬線的電阻

$$R = \rho \frac{L}{A}$$

R =電阻,  $\rho =$ 電阻係數

L =長度,A =截面積

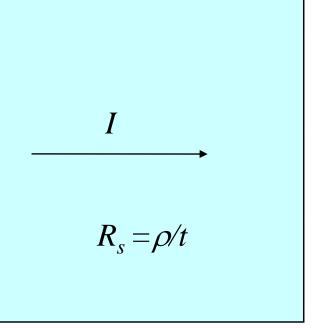

### 薄片電阻的概念

運用電流 I 和電壓 V,

電阻:  $R = V/I = \rho L/(wt)$

對長方形的電線, L = w, 所以  $R = \rho/t = R_s$

單位  $R_s$ : 每平方歐姆  $(\Omega/\Box)$

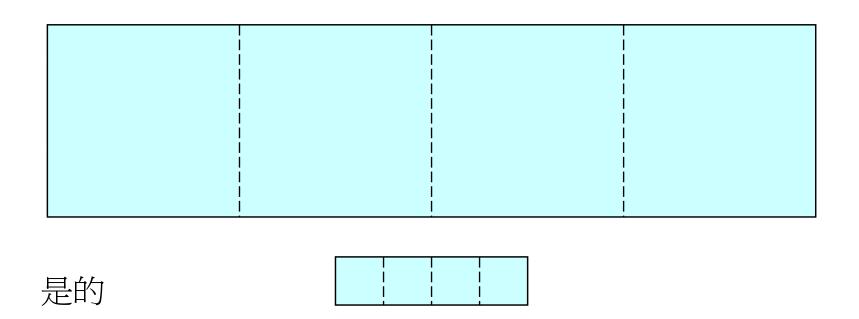

# 薄片電阻

你確定他們的 阻抗是一樣的 嗎?

$$R_s = \rho/t$$

### 薄片電阻

兩條傳導線都是用相同的金屬薄膜及相同的長寬比來圖案化,他們的線電阻是否一樣?

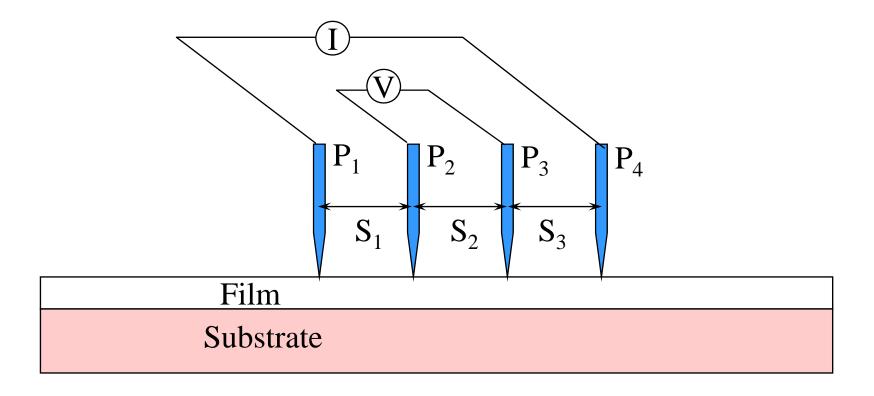

#### 四點探針

- 被用來量測薄片電阻的工具

- 一個電流被施加在兩個探針之間,而電壓則在另兩個探針之間被量測

- 假如電流 I 在  $P_1$  和  $P_4$  之間,則 $R_s$  = **4.53** V/I, 在此V 是  $P_2$  and  $P_3$ 之間的電壓

- 假如電流 I 加在  $P_1$  and  $P_3$ 之間,  $R_s = 5.75 \ V/I$ , 在此V 是 $R_2$  and  $R_4$ 之間的電壓

- 這兩個方程式都假設在薄膜區域無線大的條件下

# 四點探針量測

# 金屬化學氣相沉積法 CVD

- 廣泛地運用來沉積金屬

- 好的階梯覆蓋和間隙填充能力

- 可以填充微小的接觸窗口以使金屬連接在一 起

- 比PVD金屬薄膜有較差的品質和較高的 電阻率

- 作爲栓塞與局部連線

- 不用在長距離連線

#### 金屬 CVD

- 鎢,矽化鎢,鈦.氮化鈦

- 加熱製程,外在的熱量會提供化學反應所需的自由能(Free energy)

- 射頻單元 (RF Unit) 主要用在製程反應室 的電漿清潔過程上

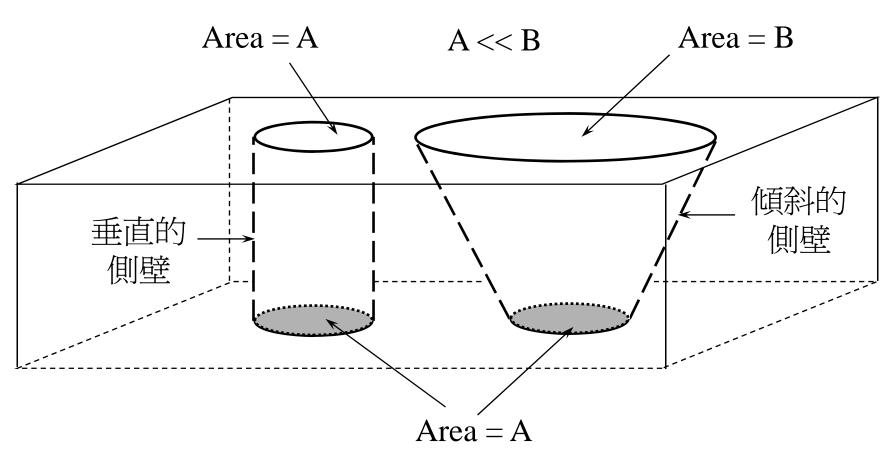

# 垂直與傾斜式的接觸窗口

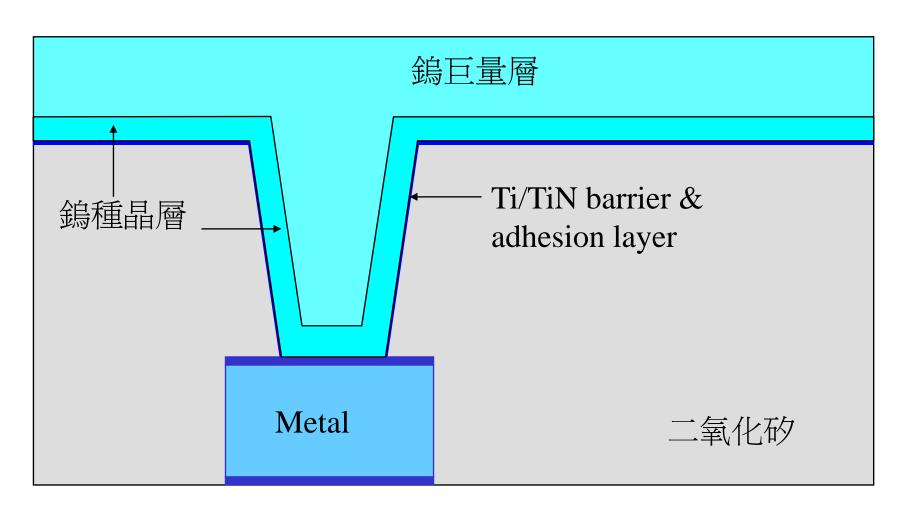

# 鎢種晶層和巨量層

#### PVD

- 固態材料氣態化

- 加熱和濺鍍

- 蒸氣在基片表面上凝結

- 金屬化的重要部分

#### PVD vs. CVD

- PVD 物理氣相沉積

- CVD 化學氣相沉積

#### PVD vs. CVD: 源材料

• PVD

固體材料

• CVD

氣體或蒸氣

# PVD 方法

- 蒸鍍

- 濺鍍

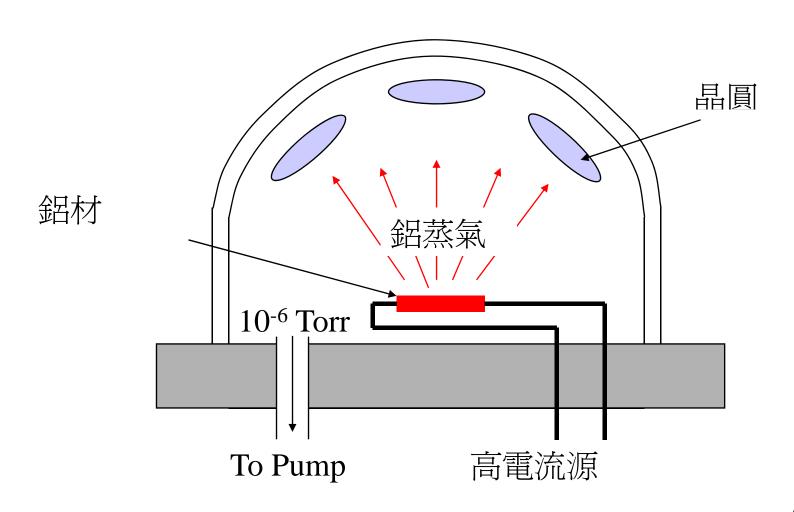

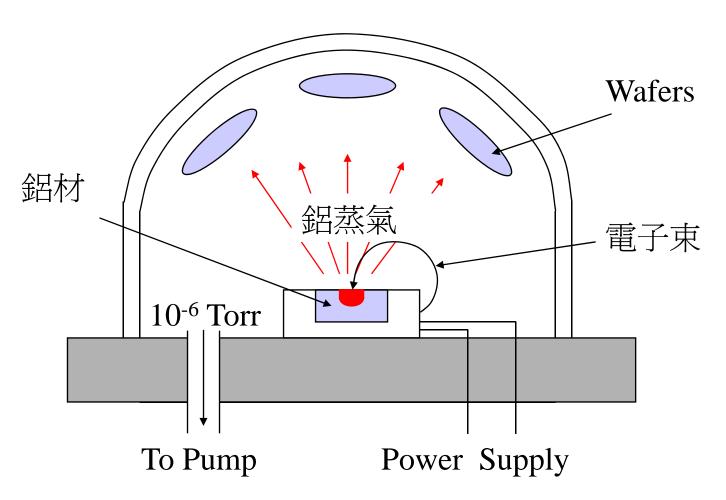

## PVD 方法:蒸鍍

- 細線

- 迅速加熱基板

- 電子束

#### 熱蒸鍍器

# 電子束蒸鍍

## PVD 方法: 濺鍍

- 直流電極

- 射頻電極

- 磁電管

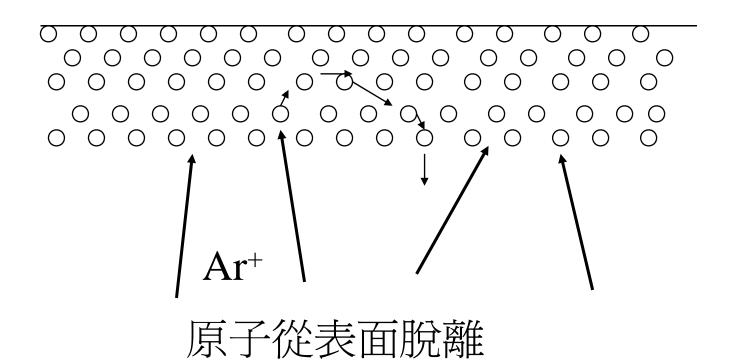

#### 濺鍍

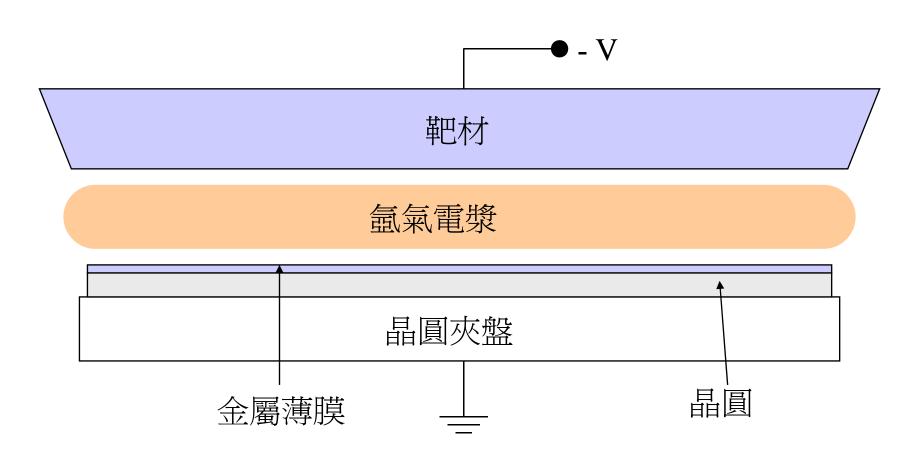

## 直流濺鍍系統

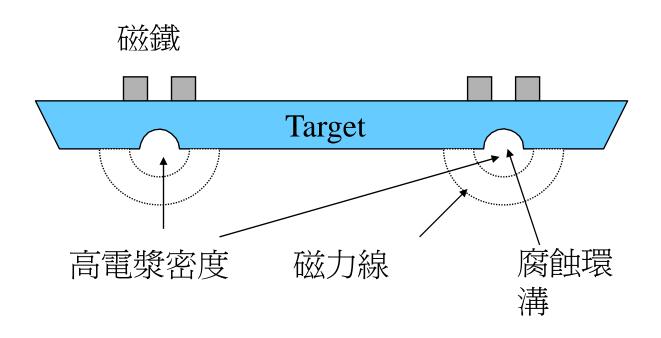

## 磁控濺鍍系統

## 磁控濺鍍

- 最廣泛運用的 PVD 系統

- 較多的濺鍍凝聚

- 較好的均勻性

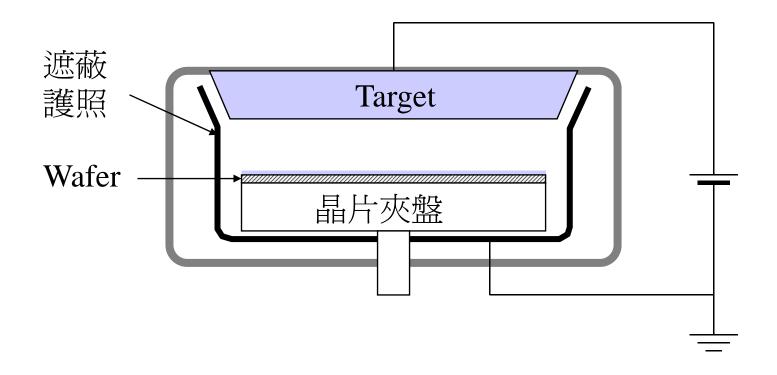

# PVD 遮蔽護罩裝置

### 氫氣的運用

- 濺鍍沉積

- 濺鍍蝕刻

- 預洗是在金屬沉積以前移除原生氧化層

- 填充電介質裂口開始尖端

- 圖案化蝕刻

- 電介質增加轟擊和產生損傷

## 氫氣的特性

- 惰性

- 相對重的

- 充足

- 大氣成分約 1%

- 低成本

### 濺鍍 VS蒸鍍

#### 濺鍍

- 純薄膜

- 較好的均勻性

- 單晶格晶圓,較好的製程控制

- 大晶粒晶圓

#### 蒸鍍

- 較不純

- 批量製程

- 較便宜工具

#### PVD 真空設備

- 在真空反應室牆壁上的殘留氣體 水, ...

- 水可以和鋁反應形成  $Al_2O_3$

- 影響局部連線的傳導率

- 唯一脫乾水的方法: 到達極真空, 10-9 Torr

### PVD 真空設備

- 載貨部分: 10<sup>-6</sup> Torr

- 轉換反應室: 10<sup>-7</sup> to 10<sup>-8</sup> Torr

- 沉積反應室: 10<sup>-9</sup> Torr

#### PVD 真空幫浦

- 濕式幫浦 (油擴散幫浦): 大氣到 10<sup>-3</sup> Torr, 逐步淘汰

- 粗抽幫浦: 大氣到 10-5 Torr

- 渦輪幫浦: 大氣10<sup>-2</sup> to 10<sup>-7</sup> Torr

- 冷凝幫浦:大氣到 10<sup>-10</sup> Torr

- 離子幫浦:大氣到 10-11 Torr

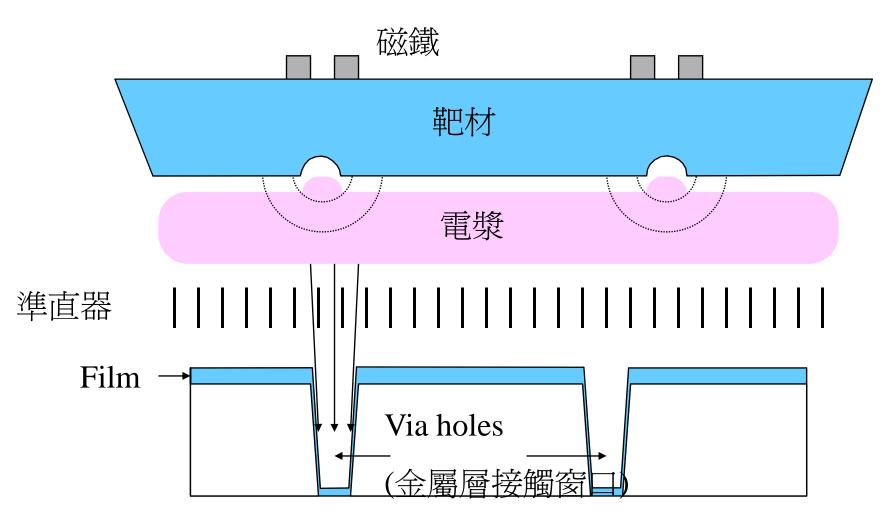

## 準直式濺鍍

- 使用在鈦或氮化鈦沉積

- 準直式容許金屬原子或分子主要以垂直方向移動

- 到達深且窄的接觸窗/金屬層間的底部

- 增加底部階梯覆蓋

## Collimated (準直式) Sputtering

#### 銅

- 比鋁傳導率好

- 較高的速度且較低功率損失

- 較高的電遷移阻抗

- 在砂和二氧化砂中擴散速率很高,造成重度金屬擴散,需要擴散阻擋層

- 不易進行乾蝕刻,缺易揮發性的無機銅化合物

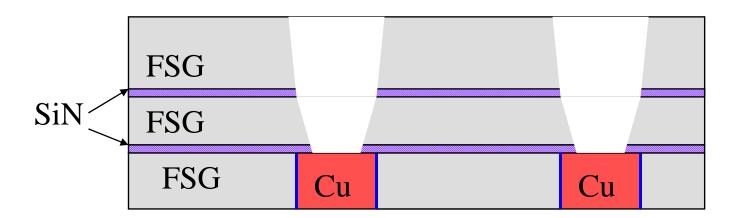

#### 銅

- CMP 製程替銅連線舖了一條路

- Ta 或 TaN 當阻擋層

- 開始使用在 IC 結構上

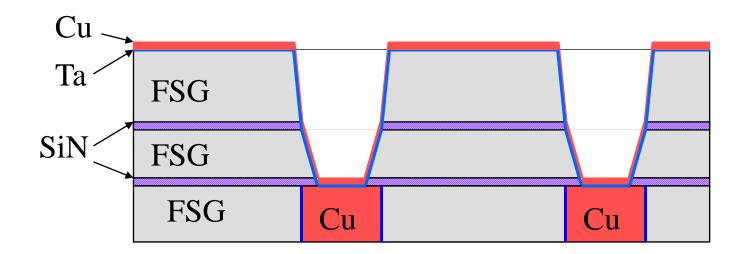

#### 銅

- 預先沉積的清洗步驟上

- PVD 阻擋層 (Ta 或 TaN, 或兩者都有)

- PVD 銅種晶層

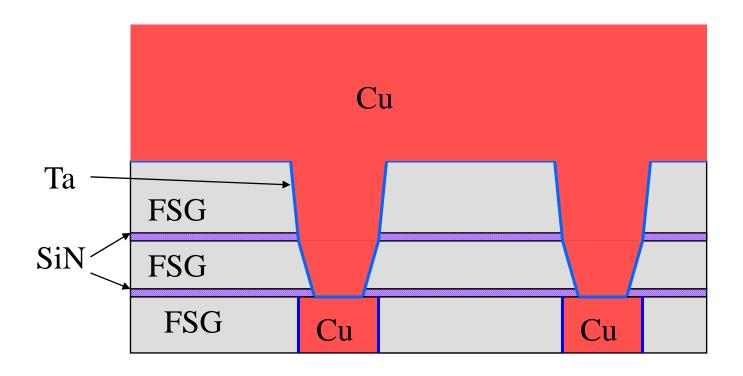

- 電化學電鍍法沉積巨量銅

• 熱退火增加傳導率

# 沉積前清洗

## PVD沉積Ta阻擋層與銅種晶層

## 電化學電鍍銅,然後退火

# 化學機械研磨銅和鉭, CVD 沉積氮化矽

#### Pre-clean (預洗)

- 氫氣濺射蝕刻用在預積的清洗步驟上

- 經常被使用

- 由於濺鍍導致銅污染

- 化學式預洗 (Chemical pre-clean )

- H<sub>2</sub>和 He 電漿

- 氫的還原化學式(取代氧化銅的氧)

$$4 H + CuO_2 \rightarrow Cu + 2 H_2O$$

### 阻擋層

- 銅擴散至矽會導致原件損害

- 需要阻擋層

- Ti, TiN, Ta, TaN, W, WN,

- 通常使用幾百埃厚度的鉭

- 在將來, 銀和氮化銀的結合

#### 銅種晶層

- PVD 銅種晶層 (500 to 2000 Å)

- 提供成核點以形成巨量銅的晶粒和薄膜

- 沒有種晶層

- 不會有沉積

- 或沉積的量跟均匀性很差

### 銅種晶層

- 銅蒸氣可以輕易的被離子化

- 低壓,長的平均自由路徑

- 銅離子可以被拋入金屬層間接觸窗口和 溝槽內

- 好的階梯覆蓋和平滑薄膜表面

- 非常窄接觸窗口, PVD 銅由於他的階梯覆蓋不好,導致有問題

- CVD 銅製程可能被需要

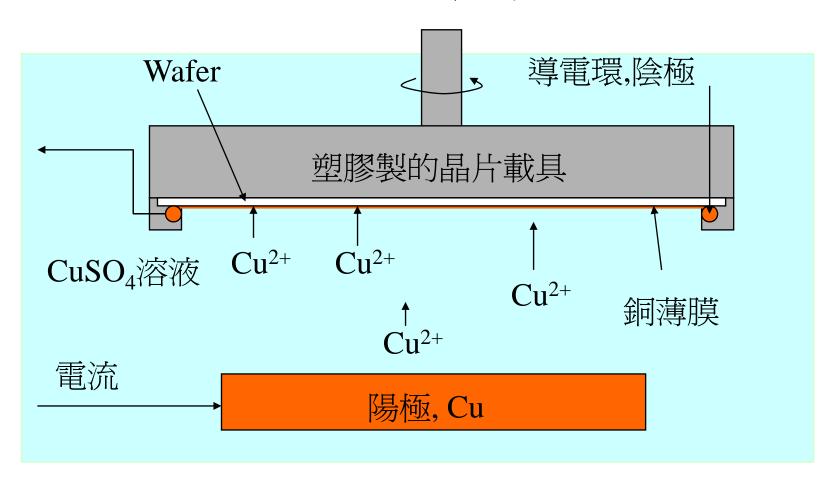

### 電化學電鍍法(ECP)

- 老技術

- 仍然在硬體,玻璃,汽車,電子和五金被使用

- 近來引入 IC 工業

- 巨量銅沉積

- 低溫製程

- 與低介電常數材料可以兼容

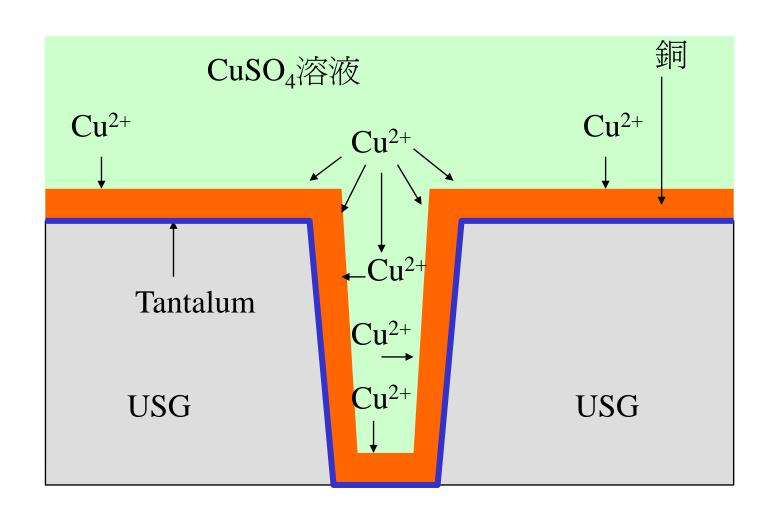

### 電化學電鍍法(ECP)

- CuSO<sub>4</sub> 溶液

- 銅製陽極

- 晶圓表面有銅種晶層當陰極

- 固定電流

- Cu<sup>2+</sup> 離子擴散和沉積在晶圓表面

## 銅電鍍製程

## 接觸窗口和導線填充

- 為達到較好的間隙覆蓋,大量的正向脈衝電流以及少量的反向脈衝電流被交替的使用

- 反向電流移除銅,以減少洞口(Overhang) 的懸凸物

- 類似沉積/蝕刻/沉積製程

- 添加物可減少在金屬層間接觸窗口角落上的沉積以改善填充能力

## 電鍍法的接觸窗口填充